# **TMC2302A Image Manipulation Sequencer** 40 MHz

# Features

· Asynchronous loading of control parameters

SEMICONDUCTOR IM

- Rapid (25ns per pixel) rotation, warping, panning, and scaling of images

- Three-dimensional image addressing capability

- General third-order polynomial transformations in two dimensions on-chip

- Three-dimensional transformation of up to order 1.5 also supported

- · Flexible, user-configurable pixel datapath timing structure

- Static convolutional filtering of up to 16 x 16 Pixel (onepass), 256 x 256 pixel (two-pass) or 256 x 256 x 256 pixel (three-pass) windows

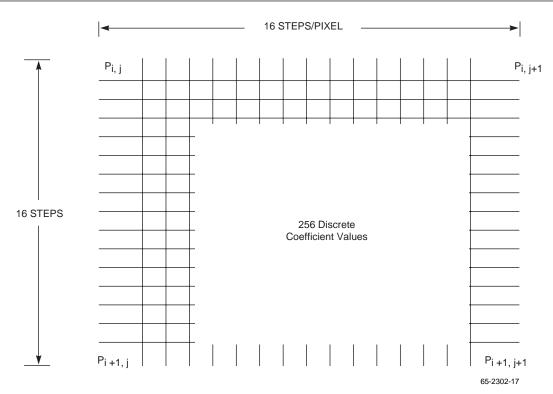

- · User-selectable source image subpixel resolution of  $2^{-8}$  to  $2^{-16}$

- Pin-compatible upgrade to TMC2302

- 24-bit (optional 36-bit) positioning precision within the source image space, 48-bit internal precision

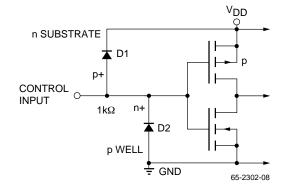

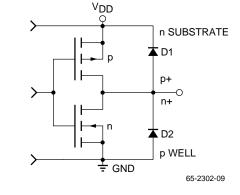

- Low power CMOS process

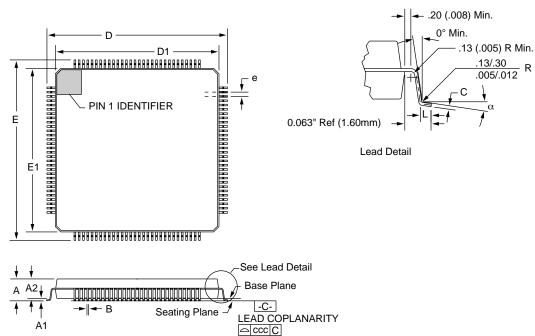

- Available in a 120-pin Plastic Pin Grid Array and 120-lead Metric Quad Flat Pack

# Applications

- · High-performance video special-effects generators

- Guidance systems

- Image recognition •

- Robotics

- High-precision image registration

## Description

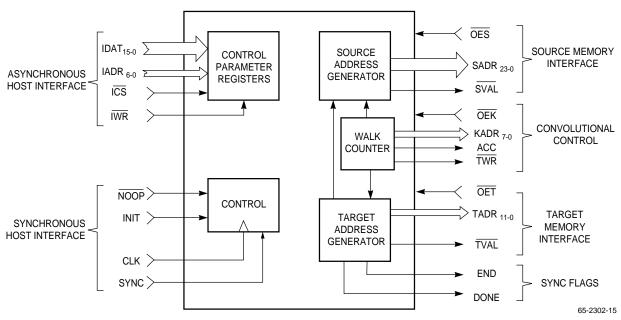

The TMC2302A, a pin-compatible replacement for the TMC2302, is a high-speed self-sequencing address generator which supports image manipulations such as rotation, rescaling, warping, filtering, and resampling. It remaps the pixel locations of a target (display) space back into those of a source image space. The degree and type of image manipulation is determined by the remapping selected.

To remap from the target to the source space, this integrated circuit computes a series of polynomials of the target space coordinates, based on user-assigned coefficients. Two TMC2302A chips can generate third-order warps of a twodimensional image, whereas three can second-order warp a three-dimensional image.

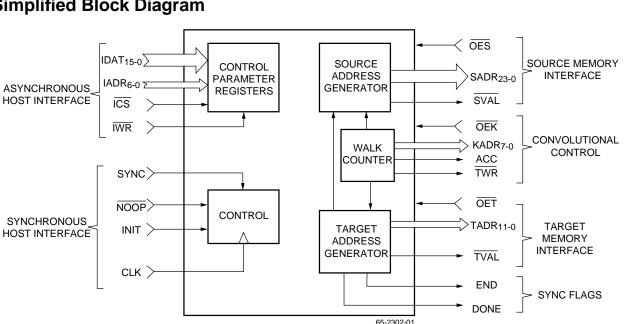

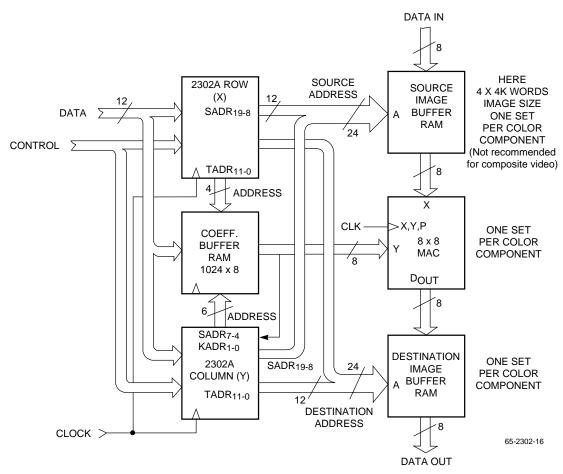

# Simplified Block Diagram

A system based on two TMC2302As can nearest-neighbor resample a two-dimensional 512 x 512 pixel image in 6.5 milliseconds, translating, rotating, or warping it, depending on the user-selected transformation parameters. A complete bilinear interpolation of the sample image can be completed in 26 milliseconds (or 6.5ms with a TMC2246A companion chip), while a nearest-neighbor resampling of a 3D image 128 pixels on a side takes only 53 milliseconds with three TMC2302As. Image resampling speed is independent of angle of rotation, degree of warp, or amount of zoom specified.

The TMC2302A can process image data fields with up to 24 bits of binary resolution ( $2^{24}$  pixels) per dimension, with 0 to 16-bit subpixel resolution.

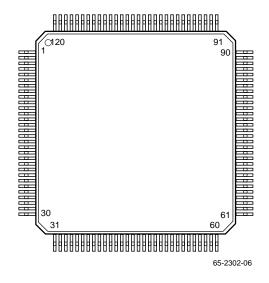

Along with the original Plastic Pin Grid Array (PPGA) package, the TMC2302A is offered in a 120-lead Metric Quad FlatPack (MQFP) as well. All TMC2302 electrical, functional, and environmental specifications are improved or remain unchanged in the TMC2302A.

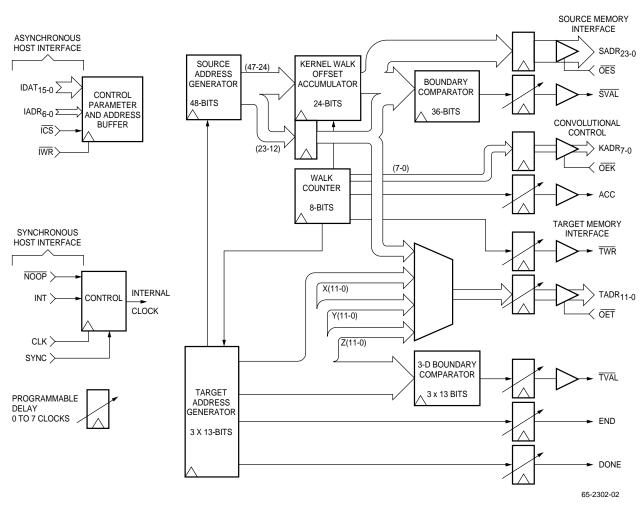

## **Block Diagram**

#### **Functional Description**

#### **General Information**

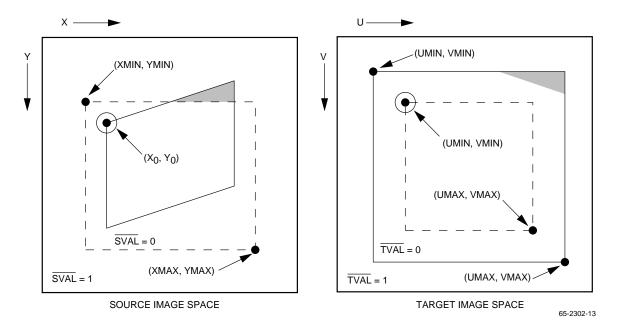

(XMIN, YMIN) >

The TMC2302A is a versatile, high-performance address generator which can control, under user direction, filtering or remapping of two or three-dimensional images by resampling them from one set of Cartesian coordinates (x, y, z)into a new, transformed set (u, v, w). Most applications utilize two identical devices for two-dimensional, or three devices for three-dimensional, image processing. The host CPU initializes the system by loading the input image buffer RAM with the source image pixel data and the TMC2302As with the image transformation and system configuration control parameters. These parameters are loaded by a separate, asynchronous input clock. The IMS-based system then executes the entire transformation as programmed, generating a DONE flag upon completion of the transform. The user can program the chip to repeat the transform continuously or to halt at the end.

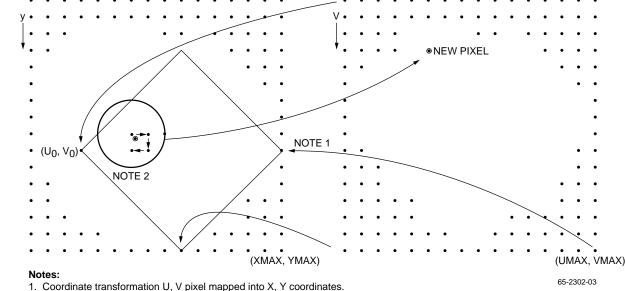

The IMSs continuously compute the target bit plane (u, v) or bit space addresses (u, v, w) in typical line-by-line, rasterscan serial sequence. For each output pixel address, they compute the corresponding remapped source image coordinates, each of whose upper 24 bits become the source bit plane addresses (x, y). An additional lower twelve bits are available through the target address port in the optional extended address mode. Source image addresses may be generated at up to 40MHz, with the corresponding target image addresses then appearing at up to (40/k)MHz, where "k" is the size of the interpolation kernel implemented. In the two-IMS system, one TMC2302A computes the horizontal coordinates x and u while the other generates the y and v

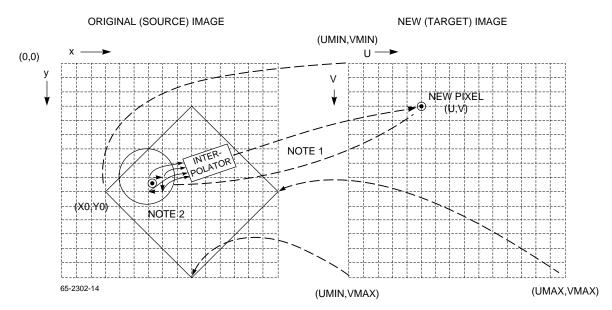

-ORIGINAL (SOURCE) IMAGE

(vertical) addresses. In a three-dimensional system, one additional IMS would provide the z and w (depth or time) coordinates.

To support a wide range of image transformations, the "row" or x/u device implements a 16-term polynomial of the form:

x = a + bu + cu<sup>2</sup> + du<sup>3</sup> + ev + fvu + gvu<sup>2</sup> + hvu<sup>3</sup> + iv<sup>2</sup>+ jv<sup>2</sup>u + kv<sup>2</sup>u<sup>2</sup> + lv<sup>2</sup>u<sup>3</sup> + mv<sup>3</sup> + nv<sup>3</sup>u + ov<sup>3</sup>u<sup>2</sup> + pv<sup>3</sup>u<sup>3</sup>

where "a" through "p" are the user-defined image transformation parameters. The TMC2302A steps sequentially through the pixels within a user-defined rectangle in the target image space, computing the "old" source image address (x, y, z) corresponding to each "new" target image pixel (u, v, w). User-programmable flags are available to indicate when the source and target image addresses have fallen outside of a defined rectangular area, simplifying the generation of complex images or image windows. Here, u = U-UMIN and v = V-VMIN, where (u,v) is the target address output by the TMC2302A.

In the three-dimensional mode, the x/u transformation equation is:

x = a + bu + ev + kw + fuv + ivw + luw + juvw

See "The Image Transformation Polynomial" section of the Applications Discussion.

NEW (TARGET)

(UMIN, VMIN)

T. Coordinate transformation 0, v pixer mapped into X, F coordinates.

2. Bilinear pixel interpolation walk. New U, V pixel intensity calculated from surrounding X, Y pixel neigborhood.

Figure 1. Image resampling geometry showing two-dimensional image rotation and expansion

The TMC2302A utilizes an external multiplier-accumulator or interpolator, connected to the system clock, to calculate the interpolated pixel value for each color. The products of the original source image pixel values surrounding the remapped pixel location (interpolation kernel) and the appropriate weights stored in the coefficient lookup table are summed. The resulting new interpolated image pixel value is then stored in the corresponding (u, v, w) memory location in the target image memory buffer. Next, the target image address is incremented by one in the "u" direction until UMAX is reached (end of line), when u is reset to UMIN, and the v counter is incremented to give the first pixel location in the next line. The process is repeated, proceeding line-by-line through the image, until VMAX is reached. In the case of three-dimensional images, the IMS system also steps through each page in the image, incrementing in the "w" direction with the completion of each image plane until WMAX is reached, and the transformation is complete.

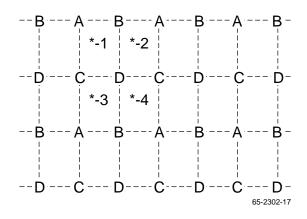

The Image Manipulation Sequencer can support any nearestneighbor, bilinear interpolation, or cubic convolution resampling. Interpolation kernels of more than one pixel require an external interpolation coefficient lookup table and multiplieraccumulator or multiple multiplier array. One, two, and three-pass algorithms are supported. For each output point in a typical two-dimensional single-pass static image filter, the TMC2302A implements a spiralling pixel resampling algorithm, "walking" around the resampling neighborhood in two dimensions and generating the appropriate coefficient table addresses to sum up the interpolated pixel value in the external pixel interpolator. At the end of each walk, the TMC2302A will advance one pixel along the output scan line and then execute the walk for that next pixel. When performing multiple-pass interpolation, the TMC2302A system proceeds along only one dimension per pass, which requires dimensionally separable, preferably orthogonal, coefficients.

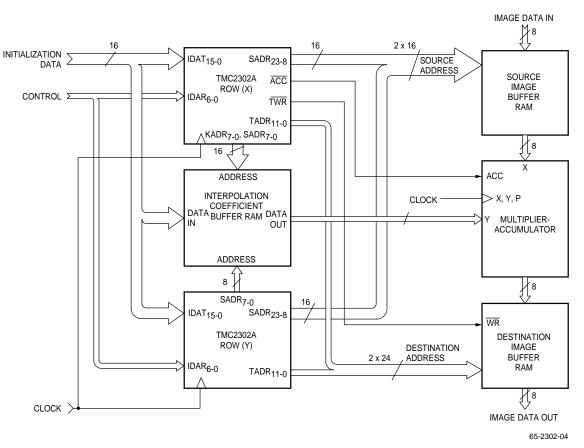

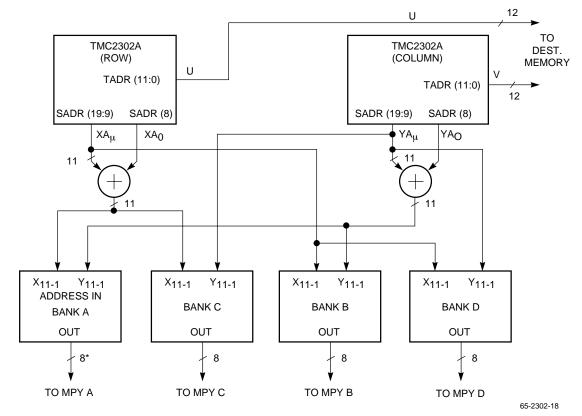

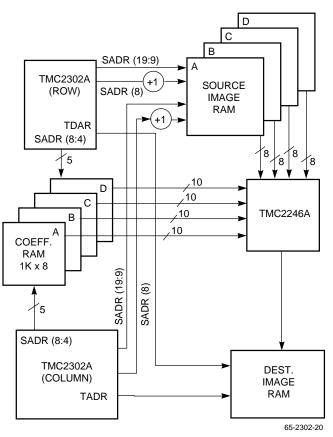

A basic, two-dimensional TMC2302A-based system is shown in Figure 2. In this typical arrangement, two Image Manipulation Sequencers process the image. The only other components needed beyond the source and target image buffer memories are a multiplier-accumulator or pixel interpolator such as the TMC2246A Image Mixer or TMC2250A Matrix Multiplier, and the Interpolation Coefficient Lookup Table RAM or ROM.

# **Pin Assignments**

#### 120 Pin Plastic Pin Grid Array, PPGA

|   | 1 | 2 | 3 | 4 | 5   | 6 | 7             | 8 | 9 | 10 | 11 | 12 | 13 |  |

|---|---|---|---|---|-----|---|---------------|---|---|----|----|----|----|--|

| Α | 。 | 0 | 0 | 0 | 0   | 0 | o             | 0 | 0 | 0  | 0  | 0  | 0  |  |

| в | 0 | 0 | 0 | 0 | 0   | 0 | 0             | 0 | 0 | 0  | 0  | 0  | 0  |  |

| С | o | 0 | 0 | 0 | ο   | 0 | 0             | 0 | 0 | 0  | 0  | 0  | 0  |  |

| D | 0 | 0 | 0 | × | KE1 | , |               |   |   |    | 0  | 0  | 0  |  |

| Е | o | 0 | 0 |   | NE  | ſ |               |   |   |    | 0  | 0  | 0  |  |

| F | 0 | 0 | 0 |   |     | - | 14            |   |   |    | 0  | 0  | 0  |  |

| G | o | 0 | 0 |   |     |   | op V<br>avity |   |   |    | 0  | 0  | 0  |  |

| н | 0 | 0 | 0 |   |     |   |               |   |   |    | 0  | 0  | 0  |  |

| J | 0 | 0 | 0 |   |     |   |               |   |   |    | 0  | 0  | 0  |  |

| κ | 0 | 0 | 0 |   |     |   |               |   |   |    | 0  | 0  | 0  |  |

| L | 0 | 0 | 0 | 0 | 0   | 0 | 0             | 0 | 0 | ο  | 0  | 0  | 0  |  |

| М | 0 | 0 | 0 | 0 | 0   | 0 | 0             | 0 | 0 | ο  | 0  | 0  | 0  |  |

| Ν | 0 | 0 | 0 | 0 | 0   | 0 | 0             | 0 | 0 | 0  | 0  | 0  | 0  |  |

|   |   |   |   |   |     |   |               |   |   |    |    |    |    |  |

65-2302-05

| Pin | Name               | Pin | Name               | Pin | Name              | Pin | Name               |

|-----|--------------------|-----|--------------------|-----|-------------------|-----|--------------------|

| A1  | GND                | C5  | SADR <sub>19</sub> | G11 | GND               | L10 | DONE               |

| A2  | SADR <sub>16</sub> | C6  | SADR <sub>22</sub> | G12 | Vdd               | L11 | Vdd                |

| A3  | SADR17             | C7  | IADR5              | G13 | IDAT <sub>0</sub> | L12 | GND                |

| A4  | Vdd                | C8  | IADR1              | H1  | SADR5             | L13 | NOOP               |

| A5  | SADR <sub>21</sub> | C9  | IDAT <sub>14</sub> | H2  | SADR <sub>4</sub> | M1  | ACC                |

| A6  | OES                | C10 | IDAT <sub>10</sub> | H3  | GND               | M2  | OEK                |

| A7  | IADR <sub>6</sub>  | C11 | GND                | H11 | GND               | M3  | KADR <sub>6</sub>  |

| A8  | IADR <sub>3</sub>  | C12 | GND                | H12 | V <sub>DD</sub>   | M4  | KADR <sub>4</sub>  |

| A9  | IADR <sub>0</sub>  | C13 | IDAT <sub>6</sub>  | H13 | SYNC              | M5  | KADR <sub>2</sub>  |

| A10 | IDAT <sub>15</sub> | D1  | SADR11             | J1  | SADR <sub>3</sub> | M6  | OET                |

| A11 | IDAT <sub>12</sub> | D2  | SADR <sub>12</sub> | J2  | SADR <sub>2</sub> | M7  | TADR <sub>0</sub>  |

| A12 | IDAT <sub>9</sub>  | D3  | GND                | J3  | Vdd               | M8  | TADR <sub>3</sub>  |

| A13 | V <sub>DD</sub>    | D11 | VDD                | J11 | VDD               | M9  | TADR <sub>6</sub>  |

| B1  | SADR <sub>14</sub> | D12 | IDAT <sub>5</sub>  | J12 | CLK               | M10 | TADR <sub>9</sub>  |

| B2  | SADR <sub>15</sub> | D13 | IDAT <sub>4</sub>  | J13 | IWR               | M11 | GND                |

| B3  | V <sub>DD</sub>    | E1  | SADR <sub>9</sub>  | K1  | SADR <sub>1</sub> | M12 | GND                |

| B4  | SADR <sub>18</sub> | E2  | SADR <sub>10</sub> | K2  | SADR <sub>0</sub> | M13 | TVAL               |

| B5  | SADR <sub>20</sub> | E3  | GND                | K3  | GND               | N1  | GND                |

| B6  | SADR <sub>23</sub> | E11 | GND                | K11 | Vdd               | N2  | KADR7              |

| B7  | IADR4              | E12 | IDAT <sub>3</sub>  | K12 | INIT              | N3  | KADR <sub>5</sub>  |

| B8  | IADR <sub>2</sub>  | E13 | IDAT <sub>2</sub>  | K13 | GND               | N4  | KADR <sub>3</sub>  |

| B9  | ICS                | F1  | SADR7              | L1  | SVAL              | N5  | KADR <sub>1</sub>  |

| B10 | IDAT <sub>13</sub> | F2  | SADR <sub>8</sub>  | L2  | V <sub>DD</sub>   | N6  | TWR                |

| B11 | IDAT <sub>11</sub> | F3  | Vdd                | L3  | NC                | N7  | TADR1              |

| B12 | IDAT <sub>8</sub>  | F11 | Vdd                | L4  | Vdd               | N8  | TADR <sub>2</sub>  |

| B13 | IDAT7              | F12 | GND                | L5  | GND               | N9  | TADR5              |

| C1  | SADR <sub>13</sub> | F13 | IDAT <sub>1</sub>  | L6  | KADR <sub>0</sub> | N10 | TADR7              |

| C2  | V <sub>DD</sub>    | G1  | SADR <sub>6</sub>  | L7  | V <sub>DD</sub>   | N11 | TADR <sub>10</sub> |

| C3  | V <sub>DD</sub>    | G2  | GND                | L8  | TADR4             | N12 | TADR <sub>11</sub> |

| C4  | GND                | G3  | V <sub>DD</sub>    | L9  | TADR8             | N13 | ENDD               |

#### Pin Assignments (continued)

#### 120 Lead Metric Quad Flat Pack, MQFP

| Pin | Name               | Pin | Name               | Pin | Name              | Pin | Name               |

|-----|--------------------|-----|--------------------|-----|-------------------|-----|--------------------|

| 1   | Vdd                | 31  | OEK                | 61  | Vdd               | 91  | GND                |

| 2   | SADR15             | 32  | KADR7              | 62  | GND               | 92  | IDAT <sub>8</sub>  |

| 3   | SADR <sub>14</sub> | 33  | V <sub>DD</sub>    | 63  | TVAL              | 93  | IDAT <sub>9</sub>  |

| 4   | GND                | 34  | KADR <sub>6</sub>  | 64  | V <sub>DD</sub>   | 94  | IDAT <sub>10</sub> |

| 5   | V <sub>DD</sub>    | 35  | KADR <sub>5</sub>  | 65  | GND               | 95  | IDAT <sub>11</sub> |

| 6   | SADR <sub>13</sub> | 36  | KADR4              | 66  | NOOP              | 96  | IDAT <sub>12</sub> |

| 7   | SADR <sub>12</sub> | 37  | GND                | 67  | INIT              | 97  | IDAT <sub>13</sub> |

| 8   | GND                | 38  | KADR <sub>3</sub>  | 68  | Vdd               | 98  | IDAT <sub>14</sub> |

| 9   | SADR11             | 39  | KADR <sub>2</sub>  | 69  | GND               | 99  | IDAT <sub>15</sub> |

| 10  | SADR <sub>10</sub> | 40  | KADR <sub>1</sub>  | 70  | CLK               | 100 | ICS                |

| 11  | SADR <sub>9</sub>  | 41  | KADR <sub>0</sub>  | 71  | ĪWR               | 101 | IADR <sub>0</sub>  |

| 12  | V <sub>DD</sub>    | 42  | OET                | 72  | GND               | 102 | IADR1              |

| 13  | SADR <sub>8</sub>  | 43  | TWR                | 73  | VDD               | 103 | IADR <sub>2</sub>  |

| 14  | SADR7              | 44  | TADR <sub>0</sub>  | 74  | SYNC              | 104 | IADR3              |

| 15  | GND                | 45  | Vdd                | 75  | Vdd               | 105 | IADR4              |

| 16  | Vdd                | 46  | TADR1              | 76  | GND               | 106 | IADR5              |

| _17 | SADR <sub>6</sub>  | 47  | TADR <sub>2</sub>  | 77  | IDAT <sub>0</sub> | 107 | IADR <sub>6</sub>  |

| 18  | SADR5              | 48  | TADR <sub>3</sub>  | 78  | IDAT <sub>1</sub> | 108 | OES                |

| 19  | SADR <sub>4</sub>  | 49  | TADR4              | 79  | GND               | 109 | SADR <sub>23</sub> |

| _20 | GND                | 50  | TADR5              | 80  | VDD               | 110 | SADR <sub>22</sub> |

| 21  | SADR <sub>3</sub>  | 51  | TADR <sub>6</sub>  | 81  | IDAT <sub>2</sub> | 111 | SADR <sub>21</sub> |

| 22  | SADR <sub>2</sub>  | 52  | TADR7              | 82  | IDAT <sub>3</sub> | 112 | SADR <sub>20</sub> |

| 23  | SADR1              | 53  | TADR8              | 83  | IDAT <sub>4</sub> | 113 | Vdd                |

| 24  | Vdd                | 54  | TADR <sub>9</sub>  | 84  | GND               | 114 | SADR <sub>19</sub> |

| 25  | SADR <sub>0</sub>  | 55  | TADR <sub>10</sub> | 85  | IDAT <sub>5</sub> | 115 | SADR <sub>18</sub> |

| 26  | SVAL               | 56  | TADR <sub>11</sub> | 86  | IDAT <sub>6</sub> | 116 | SADR <sub>17</sub> |

| 27  | ACC                | 57  | DONE               | 87  | IDAT <sub>7</sub> | 117 | SADR <sub>16</sub> |

| 28  | GND                | 58  | GND                | 88  | VDD               | 118 | GND                |

| 29  | V <sub>DD</sub>    | 59  | NC                 | 89  | GND               | 119 | Vdd                |

| 30  | GND                | 60  | ENDD               | 90  | Vdd               | 120 | GND                |

# **Pin Descriptions**

|          | Pin N                                                                                                     | umber                                                                                     |                                                                                                    |

|----------|-----------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|

| Pin Name | PPGA                                                                                                      | MQFP                                                                                      | Pin Function Description                                                                           |

| Power    | •                                                                                                         |                                                                                           |                                                                                                    |

| VDD      | C3, C2, F3,<br>G3, J3, L2,<br>L4, L7, L11,<br>K11, J11,<br>H12, G12,<br>F11, D11,<br>A13, A4, B3          |                                                                                           | <b>Supply Voltage.</b> The TMC2302A operates from a single +5V supply. All pins must be connected. |

| GND      | D3, E3, G2,<br>H3, K3, N1,<br>L5, M11,<br>M12, L12,<br>K13, H11,<br>G11, F12,<br>E11, C12,<br>C11, C4, A1 | 4, 8, 15, 20,<br>28, 30, 37,<br>58, 62, 65,<br>69, 72, 76,<br>79, 84, 89,<br>91, 118, 120 | Ground.                                                                                            |

|                      | Pin N                                                                                                               | umber                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

|----------------------|---------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Pin Name             | PPGA MQFP                                                                                                           |                                                                                                                           | Pin Function Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |

| Clocks               | •                                                                                                                   |                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

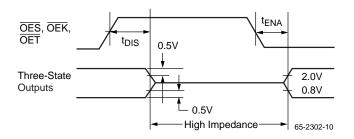

| CLK                  | J12                                                                                                                 | 70                                                                                                                        | <b>System Clock</b> . The pixel clock of the TMC2302A strobes all internal registers except the control parameter preload registers. All timing specifications except those are referenced to the rising edge of CLK.                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

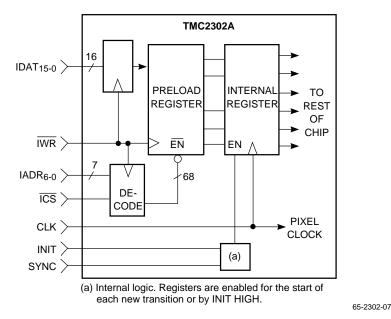

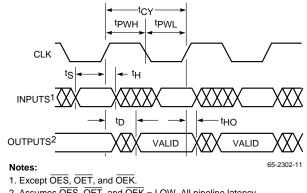

| ĪWR                  | J13                                                                                                                 | 71                                                                                                                        | <b>Input Parameter Write Clock.</b> The internal image transformation<br>and configuration control parameter registers are double buffered<br>to simplify interfacing with system controllers. Depending on the<br>state of the chip selects $\overline{\text{ICS}}$ , control words input to $\text{IDAT}_{15-0}$ and<br>the corresponding addresses presented to $\text{IADR}_{6-0}$ are strobed<br>into the outer preload registers on the rising edge of the Input<br>parameter Write clock $\overline{\text{IWR}}$ . The last parameter must be loaded<br>twice on two consecutive rising edges of $\overline{\text{IWR}}$ . |  |  |

| Inputs               | ļ                                                                                                                   | 1                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

| IDAT <sub>15-0</sub> | A10, C9,<br>B10, A11,<br>B11, C10,<br>A12, B12,<br>B13, C13,<br>D12, D13,<br>E12, E13,<br>F13, G13                  | 99, 98, 97,<br>96, 95, 94,<br>93, 92, 87,<br>86, 85, 83,<br>82, 81, 78,<br>77                                             | <b>Input Parameter Data.</b> Configuration and transformation parameter Input Data are presented, along with the appropriate input register address word IADR <sub>6-0</sub> , to the parameter Input Data port, and are latched into the preload registers on the next rising edge of $\overline{IWR}$ . Preload register updates are disabled by the chip select control $\overline{ICS}$ . See Figure 3.                                                                                                                                                                                                                       |  |  |

| IADR <sub>6-0</sub>  | A7, C7, B7,<br>A8, B8, C8,<br>A9                                                                                    | 107, 106,<br>105, 104,<br>103, 102,<br>101                                                                                | <b>Input Parameter Address.</b> The input parameter preload register currently indicated by the Input parameter register Address $IADR_{6-0}$ is loaded with the data presented to input port IDAT on the rising edge of $\overline{IWR}$ , as demonstrated in Figure 3.                                                                                                                                                                                                                                                                                                                                                          |  |  |

| Outputs              |                                                                                                                     |                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

| SADR <sub>23-0</sub> | B6, C6, A5,<br>B5, C5, B4,<br>A3, A2, B2,<br>B1, C1, D2,<br>D1, E2, E1,<br>F2, F1, G1.<br>H1, H2, J1,<br>J2, K1, K2 | 109, 110,<br>111, 112,<br>114, 115,<br>116, 117, 2,<br>3, 6, 7, 9,<br>10, 11, 13,<br>14, 17, 18,<br>19, 21, 22,<br>23, 25 | <b>Source Address.</b> The 24-bit address of one dimension (X, Y, Z) of the source image pixel value currently being resampled is output through the Source Address port SADR <sub>23-0</sub> . This port can be forced to the high-impedance state by the enable control $\overline{OES}$ .                                                                                                                                                                                                                                                                                                                                      |  |  |

| KADR <sub>7-0</sub>  | N2, M3, N3,<br>M4, N4, M5,<br>N5, L6                                                                                | 32, 34, 35,<br>36, 38, 39,<br>40, 41                                                                                      | <b>Coefficient Address.</b> The integer address steps for each dimension of the spiral interpolation walk performed by the TMC2302A, as determined by the transform parameter KERNEL, are generated by the internal walk counter and output at the Coefficient Address output port KADR <sub>7-0</sub> . This port can be forced to the high-impedance state by the enable control OEK.                                                                                                                                                                                                                                           |  |  |

|                      | Pin N                                                          | umber                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|----------------------|----------------------------------------------------------------|---------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin Name             | PPGA                                                           | MQFP                                                    | Pin Function Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| TADR <sub>11-0</sub> | N12, N11,<br>M10, L9,<br>N10, M9,<br>N9, L8, M8,<br>N8, N7, M7 | 56, 55, 54,<br>53, 52, 51,<br>50, 49, 48,<br>47, 46, 44 | <b>Target Address.</b> The 12-bit address of one dimension (U, V, W) of the target image pixel value just resampled is output through the Target Address Port TADR <sub>11-0</sub> . This port is forced into the high-impedance state by the enable control $\overrightarrow{OET}$ . TADR <sub>11-0</sub> can be delayed up to seven clock cycles after the nominal sequence shown in Table 4 by utilization of the pipeline delay parameter PIPTAD. For systems requiring greater spatial resolution in the source image than that offered by the SADR <sub>23-0</sub> alone, the Target Address Port can be reconfigured to output 12 additional LSBs of the source address by placing the device into the Extended mode, in which case the pipeline delay parameter must be set to 0 to maintain alignment with the current source address port output. See the Device Configuration and Control Parameters section. |

| Controls             | 1                                                              | 1                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| INIT                 | K12                                                            | 67                                                      | <b>Initialize.</b> The TMC2302A control logic is cleared and initialized for<br>the start of a new image transformation, and the internal working<br>registers are updated with the contents of the current control<br>parameter preload registers when the registered control input INIT<br>is HIGH. The image transformation then commences with the first<br>source image pixel address nine clocks after INIT is returned low.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| SYNC                 | H13                                                            | 74                                                      | <b>Run/Halt.</b> The user can select between continuous or one-frame operation with the registered input control SYNC. Assuming that INIT remains LOW and NOOP remains HIGH, if SYNC remains HIGH at the end of a transform the TMC2302A will begin the next image transformation without interruption. This assumes either that the user is not changing the parameter set, or that a new set of parameters has already been loaded into the preload registers midframe, prior to the beginning of the last line in the transform. If SYNC is LOW during the last clock cycle of a transform parameter set during the first clock of the final line of the transform, and halt in the state set on the first clock cycle of the next transform. These outputs are held until SYNC is again brought HIGH, and operation resumes on the next clock. See Figure 5.                                                         |

| ICS                  | B9                                                             | 100                                                     | <b>Input Parameter Chip Select.</b> The input parameter preload register write clock IWR, and thus the preloading of all configuration and transformation parameters, is disabled on the next clock when the registered Input parameter Chip Select input is HIGH. When ICS returns LOW, they are enabled on the next clock. See Figure 3.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| ACC                  | M1                                                             | 27                                                      | Accumulate. The external pixel interpolator or multiplier-<br>accumulator is initialized for a new accumulation of products by the<br>registered Accumulator Control output ACC. On the first cycle of<br>each interpolation walk, this output goes LOW for one cycle,<br>effectively clearing the register by loading in only the first new<br>resampled pixel value. When performing nearest-neighbor<br>resampling, this control will remain LOW throughout the entire<br>transform. This output can be delayed up to seven clock cycles<br>after the nominal sequence shown in Table 4 by the pipeline delay<br>parameter PIPACC. See the Device Configuration and Control<br>Parameters section.                                                                                                                                                                                                                    |

|          | Pin Number |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|----------|------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin Name | PPGA       | MQFP | Pin Function Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| TWR      | N6         | 43   | <b>Target Memory Write Enable.</b> On the last cycle of each interpolation walk, the Target Write Enable goes LOW for one clock cycle, returning HIGH for all but the last cycle of the next walk. When performing nearest-neighbor resampling, this control will remain LOW throughout the entire transform. This output can be forced to the high-impedance state by the enable control OET, and can be delayed up to seven clock cycles after the nominal sequence shown in Table 4 by the pipe-line delay parameter PIPTWR. See the Device Configuration and Control Parameters section.                                                                                                                                                                                                                                                                                                                                  |

| NOOP     | L13        | 66   | <b>No Operation.</b> Assuming that INIT remains LOW, the internal system clock of the TMC2302A will be disabled on the next clock, halting the current transform, when the registered control input NOOP goes LOW. When NOOP returns HIGH, normal operation resumes on the next clock. This control does not affect the loading of the configuration and transformation parameter preread registers.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

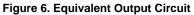

| OES      | A6         | 108  | <b>Source Address Output Enable.</b> The source address port SADR <sub>23-0</sub> is enabled when the asynchronous output enable $\overline{OES}$ is LOW. When $\overline{OES}$ is HIGH, the port is in the high-impedance state.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| OEK      | M2         | 31   | <b>Coefficient Address Output Enable.</b> The interpolation coefficient address port KADR <sub>7-0</sub> is enabled when the asynchro- nous output enable OEK is LOW. When OEK is HIGH, the port is in the high-impedance state.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| OET      | M6         | 42   | Target Address Output Enable. The target address port TADR11. $_0$ and target write enable TWR are enabled when theasynchronous Target Output Enable OET is LOW. When OET isHIGH, these outputs are in the high-impedance state. This controlfunctions in both the normal and extended addressing modes.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Flags    |            |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| SVAL     | L1         | 26   | <b>Source Address Valid.</b> When the current source image address component output is within the working space defined by the parameters XMIN and XMAX (or YMIN, YMAX for the column (Y/V) device or ZMIN, ZMAX for the page (Z/W) device), the Source Address Valid flag SVAL for that device is LOW. This flag will go HIGH on the clock in which the corresponding component address falls outside the defined region. In a typical system, the SVAL outputs of all IMS devices are OR'ed together to generate a global boundary violation flag. The user might then insert zeroes into the pixel interpolator to ignore that portion of the image outside the defined space, or insert a background color or image. This output can be delayed up to seven clock cycles after the nominal sequence shown in Table 4 by the pipeline delay parameter PIPSVA. See the Device Configuration and Control Parameters section. |

|            | Pin I | Number   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|------------|-------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin Name   | PPGA  | MQFP     | Pin Function Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| TVAL       | M13   | 63       | <b>Target Address Valid.</b> When the current target image addresses are within the working space defined by the parameters UMINI and UMAXI, and VMINI and VMAXI (and WMINI and WMAXI for systems processing three-dimensional images), the Target Address Valid flag TVAL for that device is LOW. This flag will go HIGH on the clock in which the current target address outputs fall outside the defined region, which must fall inside the target area defined by UMIN, UMAX, etc. Since each TMC2302A device is programmed with distinct MINI/MAXI parameters and generates a separate TVAL flag, the user may define separate two or three-dimensional target space windows for each device. TVAL can be delayed up to seven clock cycles after the nominal sequence shown in Table 4 by the pipeline delay parameters section. |

| ENDD       | N13   | 60       | <b>End of Dimension.</b> During the last pixel interpolation walk of a row (X/U device), the last row in a page (Y/V device), or the last page in a three-dimensional transform (Z/W device), the flag ENDD goes HIGH for the entire walk, indicating End of the transform in that dimension. It remains LOW otherwise. This output can be delayed up to seven clock cycles after the nominal sequence shown in Table 4 by the pipeline delay parameter PIPEND. See the Device Configuration and Control Parameters section.                                                                                                                                                                                                                                                                                                          |

| DONE       | L10   | 57       | <b>Done.</b> On the last clock cycle of the current image transform, the DONE flags on all TMC2302As go HIGH for one clock cycle. On the next clock cycle, all devices output the first addresses and control signals for the next image transform. If SYNC is LOW, the IMS system halts. If SYNC is HIGH, operation continues without interruption. See "SYNC," in the Controls section. This flag can be delayed up to seven clock cycles after the nominal sequence shown in Table 4 by the pipeline delay parameter PIPDON. Also see "PFLS," in the Device Configuration and Control Parameters section.                                                                                                                                                                                                                          |

| No Connect |       |          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| NC         | L3    | 59       | No Connect.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|            | D4    | <u> </u> | Index Pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

#### Transformation Coefficient and Configuration and Control Parameters

The TMC2302A is intended to act as a co-processor, requiring only that the user program the device to perform the image transformation desired by loading in the appropriate device configuration and transformation control parameters discussed in this section. The user then issues an "Init" command, allowing his system to run unattended until the completion of the image when a "Done" flag is generated to inform the host system.

The capabilities and flexibility of the TMC2302A Image Manipulation Sequencer are apparent when reviewing the following tables which define the transformation coefficient and configuration and control parameters. These tables are broken up into two separate groups. The first parameters discussed are the control words which select the dimension calculated, the functional configuration of each device, the working space in which they will operate, the size of the interpolation kernel desired, and the timing of the various address and control signals involved in handling the pixel data pipeline. The second parameters are the polynomial transform coefficients used in performing image manipulation. The TMC2302A utilizes three levels of internal 48-bit accumulators to calculate these values by forward difference accumulation, generating no significant cumulative spatial error for most applications. The user must be aware that all internal parameter and coefficient registers must be set by the user, including resetting after powerup any unused control words or coefficients.

As mentioned above, the TMC2302A also features userprogrammable image data pipeline configuration controls. All output signals except the source and coefficient address outputs can be individually delayed by the user up to seven clocks after the nominal system timing illustrated in Table 4. This allows the user to software-configure the TMC2302As in his system to match his pixel interpolator, image buffer, and interpolation coefficient RAM structure timing.

The user can also program the device to continue into the next image for a set number of clock cycles after the Done flag has appeared. First, this "flushes" the final resampled pixel data word through the interpolation pipeline, all the way to the target image RAM. Also, valid pixel data will then appear on the first clock of the next transform independent of the length of the pixel pipeline, incurring no lost clock cycles.

# Device Configuration and Control Parameters

| UMIN, | The memory addresses of the target image        |

|-------|-------------------------------------------------|

| VMIN, | boundaries corresponding to the top, left side, |

| WMIN  | and front page of the new image being gener-    |

|       | ated are defined in all devices of the user's   |

|       | system by the parameters UMIN, VMIN, and        |

|       | WMIN, respectively. At the beginning of the     |

|       | transformation, the initial source image coor-  |

|       | dinate $(X_0, Y_0, Z_0)$ will be mapped to this |

|       | coordinate set. The numeric format assumed      |

|       | is 12-bit unsigned binary integer.              |

|       |                                                 |

| UMAX, | The memory addresses of the target image     |

|-------|----------------------------------------------|

| VMAX, | boundaries corresponding to the bottom,      |

| WMAX  | right side, and last page of the image being |

|       | generated are defined in all devices by the  |

|       | parameters UMAX, VMAX, and WMAX,             |

|       | respectively. These values should be greater |

|       | than the UMIN/VMIN/WMIN values defined       |

|       | above. Numeric format assumed is unsigned    |

|       | 12-bit binary integer.                       |

|       |                                              |

**Note:** The parameter UMAX must exceed UMIN so as to ensure that a minimum of 5 system clock cycles in twodimensional operation, or 15 clock cycles in three-dimensional operation, pass between the periods in which these two target address values are generated. Thus in 2D nearest neighbor operation UMAX must be 5 greater than UMIN. In 2D bilinear interpolation mode (4-pixel two-dimensional kernel) the distance must be two pixels in the target image (actually enforcing a spacing of 8 system clocks).

| UMINI,<br>VMINI,<br>WMINI | The target image addresses corresponding to<br>those of the top, left side, and front page of the<br>2 or 3 dimensional region indicated by the<br>valid target address flag TVAL are UMINI,<br>VMINI, and WMINI, respectively. Thus, to<br>define a valid region beginning at "m," the<br>MINI parameter value is "m," These parame-<br>ters are assumed to be in 12-bit unsigned<br>binary integer format. Proper TVAL operation<br>requires UMIN < UMINI < UMAXI |

|---------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

UMAXI, The target image addresses one more than

VMAXI, those of the right side, bottom and back page

WMAXI of the region indicated by the valid target address flag TVAL are UMAXI, VMAXI, and WMAXI, respectively. Thus, to define a valid region ending at "n," the MAXI parameter value is "n+1". These parameters are assumed to be in 12-bit unsigned integer format.

XMIN, The source image boundaries are defined for XMAX each device by the parameters XMIN and XMAX, in the case of the row device. The column device then contains YMIN and YMAX, and the page device (in systems performing three-dimensional operations) ZMIN and ZMAX. The value of XMAX should be greater than XMIN if the boundary violation flag  $\overline{SVAL}$  is to operate correctly. These values are assumed to be in 32-bit unsigned binary integer format. PFLS The user can set the number of clock cycles that the TMC2302A continues in to the next image following the DONE flag, allowing his system to Flush all control and data pipeline paths and halt after a maximum of seven cycles. The numeric format assumed is threebit unsigned binary integer. PTAD, As mentioned above, the control signals and PDON. target image pixel addresses generated by the PEND, TMC2302A can be delayed up to seven clock PTVA. cycles after the nominal timing shown in PSVA. Table 4 by setting the appropriate Pipeline PTWR, delay word. The numeric format assumed for all delay words is three-bit unsigned binary PACC integer. **XTND** When the user sets the control bit XTND to 1, the TMC2302A operates in an extendedresolution source address bus configuration. Assuming that the user has his own raster scan generator available elsewhere to manage the flow of output pixels from the TMC2302A system, the target address output bus TADR<sub>11-0</sub> is reconfigured internally into an extension of the source address bus, as  $SADR_{11-0}$ . The original source address bus SADR<sub>23-0</sub> is then SADR<sub>35-12</sub>, providing 36 bits of spatial resolution in the source address space. An XTND of 0 puts the device in the standard 24-bit source, 12-bit target address configuration. E3D Setting this control bit to 0 indicates a two-dimensional image transform is to be performed. When the E3D is set to 1, a threedimensional image is assumed, using three TMC2302A devices. DIM The user sets each TMC2302A to operate in a specific dimension as follows:

| DIM1,0 | Dimension           |

|--------|---------------------|

| 00     | X/U (Row) Device    |

| 01     | Y/V (Column) Device |

| 10     | Z/W (Page) Device   |

| 11     | No Operation        |

MODE In systems performing the standard two-dimensional spiral interpolation walk, MODE is set to 11, indicating single-pass operation. When performing multiple-pass resampling, the user must set this two-bit control word pass-by-pass in all IMSs, to implement each pass direction. For instance, setting MODE to 00 causes the TMC2302A system to increment only in the X-direction, holding the Y (and Z) addresses constant until the end of that pixel walk. On the next pass through the image, the user sets MODE = 01, with the kernel increment in Y only. In 3D, the IMS system then proceeds again through the (U, V) target image space, walking kernels only along the Z direction.

| Mode <sub>1,0</sub> | Resampling Performed      |

|---------------------|---------------------------|

| 00                  | X-Pass                    |

| 01                  | Y-Pass                    |

| 10                  | Z-Pass                    |

| 11                  | Two-Dimension Spiral Walk |

- KERNEL This parameter determines the size of the interpolation walk performed. To implement a convolutional sum of K+1 pixels, the parameter KERNEL is set to K, up to a maximum of 255. In single-pass operation, this value must be identical in all devices, giving a square interpolation kernel. In multiple-pass operation, however, non- square kernels may be implemented, with different K values in each dimension. Or, the user could utilize a banded memory architecture in two-pass mode to access an entire row or column of a kernel in one clock, completing the entire sum in a single pass through the other dimension of the kernel. Numeric format is 8-bit unsigned integer.

- FOV The user determines the size of each step in an interpolation walk, in terms of the number of source image pixels, by setting the Field Of View control. The binary weighting of the image transformation parameters and source address must be taken into account when determining this value. See Table 6 and the Applications Discussion section. The numeric format assumed is unsigned 16-bit integer.

#### Table 1. Control Parameter Registers Binary Format (Row, Column or Page Device)

| Ac     | ldr |                     |                       |                     |                     |                       |                     |                            |                       |                     |                     |                       | Format          |                  |                       |                   |                   | L                       | .imits       |

|--------|-----|---------------------|-----------------------|---------------------|---------------------|-----------------------|---------------------|----------------------------|-----------------------|---------------------|---------------------|-----------------------|-----------------|------------------|-----------------------|-------------------|-------------------|-------------------------|--------------|

| Name   | Hex | MSE                 | 3                     |                     |                     |                       |                     |                            |                       |                     |                     |                       |                 |                  |                       |                   | LSB               | Dec                     | Hex          |

| UMIN   | 30  |                     |                       |                     |                     | 2 <sup>1</sup><br>1   | 2 <sup>1</sup><br>0 | 2 <sup>9</sup>             | 2 <sup>8</sup>        | 2 <sup>7</sup>      | 2 <sup>6</sup>      | 2 <sup>5</sup>        | 2 <sup>4</sup>  | 2 <sup>3</sup>   | 2 <sup>2</sup>        | 2 <sup>1</sup>    | 2 <sup>0</sup>    | 4095<br>0               | FFF<br>000   |

| UMAX   | 31  |                     |                       |                     |                     | 2 <sup>1</sup><br>1   | 2 <sup>1</sup><br>0 | 2 <sup>9</sup>             | 2 <sup>8</sup>        | 2 <sup>7</sup>      | 2 <sup>6</sup>      | 2 <sup>5</sup>        | 2 <sup>4</sup>  | 2 <sup>3</sup>   | 2 <sup>2</sup>        | 2 <sup>1</sup>    | 2 <sup>0</sup>    | 4095<br>0               | FFF<br>000   |

| UMINI  | 32  |                     |                       |                     |                     | 2 <sup>1</sup><br>1   | 2 <sup>1</sup><br>0 | 2 <sup>9</sup>             | 2 <sup>8</sup>        | 2 <sup>7</sup>      | 2 <sup>6</sup>      | 2 <sup>5</sup>        | 2 <sup>4</sup>  | 2 <sup>3</sup>   | 2 <sup>2</sup>        | 2 <sup>1</sup>    | 2 <sup>0</sup>    | 4095<br>0               | FFF<br>000   |

| UMAXI  | 33  |                     |                       |                     |                     | 2 <sup>1</sup><br>1   | 2 <sup>1</sup><br>0 | 2 <sup>9</sup>             | 2 <sup>8</sup>        | 2 <sup>7</sup>      | 2 <sup>6</sup>      | 2 <sup>5</sup>        | 2 <sup>4</sup>  | 2 <sup>3</sup>   | 2 <sup>2</sup>        | 2 <sup>1</sup>    | 2 <sup>0</sup>    | 4095<br>0               | FFF<br>000   |

| VMIN   | 34  |                     |                       |                     |                     | 2 <sup>1</sup><br>1   | 2 <sup>1</sup><br>0 | 2 <sup>9</sup>             | 2 <sup>8</sup>        | 2 <sup>7</sup>      | 2 <sup>6</sup>      | 2 <sup>5</sup>        | 2 <sup>4</sup>  | 2 <sup>3</sup>   | 2 <sup>2</sup>        | 2 <sup>1</sup>    | 2 <sup>0</sup>    | 4095<br>0               | FFF<br>000   |

| VMAX   | 35  |                     |                       |                     |                     | 2 <sup>1</sup><br>1   | 2 <sup>1</sup><br>0 | 2 <sup>9</sup>             | 2 <sup>8</sup>        | 2 <sup>7</sup>      | 2 <sup>6</sup>      | 2 <sup>5</sup>        | 2 <sup>4</sup>  | 2 <sup>3</sup>   | 2 <sup>2</sup>        | 2 <sup>1</sup>    | 2 <sup>0</sup>    | 4095<br>0               | FFF<br>000   |

| VMINI  | 36  |                     |                       |                     |                     | 21<br>1               | 2 <sup>1</sup><br>0 | 2 <sup>9</sup>             | 2 <sup>8</sup>        | 2 <sup>7</sup>      | 2 <sup>6</sup>      | 2 <sup>5</sup>        | 2 <sup>4</sup>  | 2 <sup>3</sup>   | 2 <sup>2</sup>        | 2 <sup>1</sup>    | 2 <sup>0</sup>    | 4095<br>0               | FFF<br>000   |

| VMAXI  | 37  |                     |                       |                     |                     | 21<br>1               | 2 <sup>1</sup><br>0 | 2 <sup>9</sup>             | 2 <sup>8</sup>        | 2 <sup>7</sup>      | 2 <sup>6</sup>      | 2 <sup>5</sup>        | 24              | 2 <sup>3</sup>   | 2 <sup>2</sup>        | 2 <sup>1</sup>    | 2 <sup>0</sup>    | 4095<br>0               | FFF<br>000   |

| WMIN   | 38  |                     |                       |                     |                     | 2 <sup>1</sup><br>1   | 2 <sup>1</sup><br>0 | 2 <sup>9</sup>             | 2 <sup>8</sup>        | 2 <sup>7</sup>      | 2 <sup>6</sup>      | 2 <sup>5</sup>        | 2 <sup>4</sup>  | 2 <sup>3</sup>   | 2 <sup>2</sup>        | 2 <sup>1</sup>    | 2 <sup>0</sup>    | 4095<br>0               | FFF<br>000   |

| WMAX   | 39  |                     |                       |                     |                     | 2 <sup>1</sup><br>1   | 21<br>0             | 2 <sup>9</sup>             | 2 <sup>8</sup>        | 2 <sup>7</sup>      | 2 <sup>6</sup>      | 2 <sup>5</sup>        | 2 <sup>4</sup>  | 2 <sup>3</sup>   | 2 <sup>2</sup>        | 2 <sup>1</sup>    | 2 <sup>0</sup>    | 4095<br>0               | FFF<br>000   |

| WMINI  | 3A  |                     |                       |                     |                     | 2 <sup>1</sup><br>1   | 2 <sup>1</sup><br>0 | 2 <sup>9</sup>             | 2 <sup>8</sup>        | 2 <sup>7</sup>      | 2 <sup>6</sup>      | 2 <sup>5</sup>        | 2 <sup>4</sup>  | 2 <sup>3</sup>   | 2 <sup>2</sup>        | 2 <sup>1</sup>    | 2 <sup>0</sup>    | 4095<br>0               | FFF<br>000   |

| WMAXI  | 3B  |                     |                       |                     |                     | 2 <sup>1</sup><br>1   | 2 <sup>1</sup><br>0 | 2 <sup>9</sup>             | 2 <sup>8</sup>        | 2 <sup>7</sup>      | 2 <sup>6</sup>      | 2 <sup>5</sup>        | 2 <sup>4</sup>  | 2 <sup>3</sup>   | 2 <sup>2</sup>        | 2 <sup>1</sup>    | 2 <sup>0</sup>    | 4095<br>0               | FFF<br>000   |

| XMINL  | 3C  | 2 <sup>1</sup><br>5 | 21<br>4               | 2 <sup>1</sup><br>3 | 2 <sup>1</sup><br>2 | 2 <sup>1</sup><br>1   | 2 <sup>1</sup><br>0 | 2 <sup>9</sup>             | 2 <sup>8</sup>        | 2 <sup>7</sup>      | 2 <sup>6</sup>      | 2 <sup>5</sup>        | 2 <sup>4</sup>  | 2 <sup>3</sup>   | 2 <sup>2</sup>        | 2 <sup>1</sup>    | 2 <sup>0</sup>    | 0                       | 00000000     |

| XMINM  | 3D  | 2 <sup>3</sup><br>1 | 2 <sup>3</sup>        | 2 <sup>2</sup><br>9 | 2 <sup>2</sup><br>8 | 2 <sup>2</sup><br>7   | 2 <sup>2</sup><br>6 | 2 <sup>2</sup><br>5        | 2 <sup>2</sup><br>4   | 2 <sup>2</sup><br>3 | 2 <sup>2</sup><br>2 | 2 <sup>21</sup>       | 2 <sup>20</sup> | 2 <sup>19</sup>  | 2 <sup>18</sup>       | 2 <sup>17</sup>   | 2 <sup>16</sup>   | 2 <sup>32</sup> -1      | FFFFFF       |

| XMAXL  | 3E  | 2 <sup>1</sup><br>5 | 21<br>4               | 2 <sup>1</sup><br>3 | 21<br>2             | 2 <sup>1</sup><br>1   | 2 <sup>1</sup><br>0 | 2 <sup>9</sup>             | 2 <sup>8</sup>        | 2 <sup>7</sup>      | 2 <sup>6</sup>      | 2 <sup>5</sup>        | 24              | 2 <sup>3</sup>   | 2 <sup>2</sup>        | 2 <sup>1</sup>    | 2 <sup>0</sup>    | 0                       | 00000000     |

| XMAXM  | 3F  | 2 <sup>3</sup><br>1 | 2 <sup>3</sup>        | 29 <sup>2</sup>     | 2 <sup>2</sup><br>8 | 2 <sup>2</sup><br>7   | 2 <sup>2</sup><br>6 | <b>2</b> <sup>2</sup><br>5 | 2 <sup>2</sup><br>4   | 2 <sup>2</sup><br>3 | 2 <sup>2</sup><br>2 | 2 <sup>21</sup>       | 2 <sup>20</sup> | 2 <sup>19</sup>  | 2 <sup>18</sup>       | 2 <sup>17</sup>   | 2 <sup>16</sup>   | 2 <sup>32</sup> -1      | FFFFFF       |

| PFLS   | 40  |                     | <b>2</b> <sup>2</sup> | 2 <sup>1</sup>      | 2 <sup>0</sup>      |                       |                     |                            |                       |                     |                     |                       |                 |                  |                       |                   |                   | 7<br>0                  | 7<br>0       |

| PTAD   | 40  |                     |                       |                     |                     | <b>2</b> <sup>2</sup> | 2 <sup>1</sup>      | 2 <sup>0</sup>             |                       |                     |                     |                       |                 |                  |                       |                   |                   | 7<br>0                  | 7<br>0       |

| PDON   | 40  |                     |                       |                     |                     |                       |                     |                            | <b>2</b> <sup>2</sup> | 2 <sup>1</sup>      | 2 <sup>0</sup>      |                       |                 |                  |                       |                   |                   | 7<br>0                  | 7<br>0       |

| PEND   | 40  |                     |                       |                     |                     |                       |                     |                            |                       |                     |                     | <b>2</b> <sup>2</sup> | 2 <sup>1</sup>  | 2 <sup>0</sup>   |                       |                   |                   | 7<br>0                  | 7<br>0       |

| PTVA   | 40  |                     |                       |                     |                     |                       |                     |                            |                       |                     |                     |                       |                 |                  | <b>2</b> <sup>2</sup> | 2 <sup>1</sup>    | 2 <sup>0</sup>    | 7<br>0                  | 7<br>0       |

| PSVA   | 41  |                     | <b>2</b> <sup>2</sup> | 2 <sup>1</sup>      | 2 <sup>0</sup>      |                       |                     |                            |                       |                     |                     |                       |                 |                  |                       |                   |                   | 7<br>0                  | 7<br>0       |

| PTWR   | 41  |                     |                       |                     |                     | <b>2</b> <sup>2</sup> | 2 <sup>1</sup>      | 2 <sup>0</sup>             |                       |                     |                     |                       |                 |                  |                       |                   |                   | 7<br>0                  | 7<br>0       |

| PACC   | 41  |                     |                       |                     |                     |                       |                     |                            | <b>2</b> <sup>2</sup> | 2 <sup>1</sup>      | 2 <sup>0</sup>      |                       |                 |                  |                       |                   |                   | 7<br>0                  | 7<br>0       |

| XTND   | 41  |                     |                       |                     |                     |                       |                     |                            |                       |                     |                     | XTND                  |                 |                  |                       |                   |                   |                         |              |

| E3D    | 41  |                     |                       |                     |                     |                       |                     |                            |                       |                     |                     |                       | E3D             |                  |                       |                   |                   |                         |              |